Theses and Dissertations

Fall 2009

# New tests and test methodologies for scan cell internal faults

Fan Yang University of Iowa

Follow this and additional works at: https://ir.uiowa.edu/etd

Part of the Electrical and Computer Engineering Commons

Copyright 2009 Fan Yang

This dissertation is available at Iowa Research Online: https://ir.uiowa.edu/etd/452

#### **Recommended Citation**

Yang, Fan. "New tests and test methodologies for scan cell internal faults." PhD (Doctor of Philosophy) thesis, University of Iowa, 2009.

https://doi.org/10.17077/etd.jpzs3510

Follow this and additional works at: https://ir.uiowa.edu/etd

Part of the Electrical and Computer Engineering Commons

# NEW TESTS AND TEST METHODOLOGIES FOR SCAN CELL INTERNAL FAULTS

by

Fan Yang

#### An Abstract

Of a thesis submitted in partial fulfillment of the requirements for the Doctor of Philosophy degree in Electrical and Computer Engineering in the Graduate College of The University of Iowa

December 2009

Thesis Supervisors: Professor Sudhakar M. Reddy Sreejit Chakravarty

#### **ABSTRACT**

Semiconductor industry goals for the quality of shipped products continue to get higher to satisfy customer requirements. Higher quality of shipped electronic devices can only be obtained by thorough tests of the manufactured components. Scan chains are universally used in large industrial designs in order to cost effectively test manufactured electronic devices. They contain nearly half of the logic transistors in large industrial designs. Yet, faults in the scan cells are not directly targeted by the existing tests. The main objective of this thesis is to investigate the detectability of the faults internal to scan cells.

In this thesis, we analyze the detection of line stuck-at, transistor stuck-on, resistive opens and bridging faults in scan cells. Both synchronous and asynchronous scan cells are considered. We define the notion of half-speed flush test and demonstrate that such new tests increase coverage of internal faults in scan cells. A new set of flush tests is proposed and such tests are applied at higher temperatures to detect scan cell internal opens with a wider range of resistances. We also propose new scan based tests to further increase the coverage of those opens. The proposed tests are shown to achieve the maximum possible coverage of opens in transistors internal to scan cells. For an asynchronous scan cell considered, two new flush tests are added to cover the faults that are not detected by the tests for synchronous scan cells. An analysis of detection of a set of scan cell internal bridging faults is described. Both zero-resistance and nonzero-resistance bridging fault models are considered. We show that the detection of some zero-resistance non-feedback bridging faults requires two-pattern tests. We classify the undetectable faults based on the reasons for their undetectability.

We also propose an enhanced logic BIST architecture that accomplishes the new flush tests we propose to detect scan cell internal opens.

The effectiveness of these new methods to detect scan cell internal faults is demonstrated by experimental results using some standard scan cells from a large industrial design.

| Abstract Approved: |                      |

|--------------------|----------------------|

| rr ····            | Thesis Supervisor    |

|                    |                      |

|                    |                      |

|                    | Title and Department |

|                    |                      |

|                    | Date                 |

|                    | Date                 |

|                    |                      |

|                    | Thesis Supervisor    |

|                    | 1                    |

|                    |                      |

|                    | Title and Department |

|                    |                      |

|                    |                      |

|                    | Date                 |

# NEW TESTS AND TEST METHODOLOGIES FOR SCAN CELL INTERNAL FAULTS

by

Fan Yang

A thesis submitted in partial fulfillment of the requirements for the Doctor of Philosophy degree in Electrical and Computer Engineering in the Graduate College of The University of Iowa

December 2009

Thesis Supervisors: Professor Sudhakar M. Reddy Sreejit Chakravarty

# Graduate College The University of Iowa Iowa City, Iowa

| CE                      | RTIFICATE OF APPROVAL                                                                                             |

|-------------------------|-------------------------------------------------------------------------------------------------------------------|

|                         | PH.D. THESIS                                                                                                      |

| This is to certify that | at the Ph.D. thesis of                                                                                            |

|                         | Fan Yang                                                                                                          |

| for the thesis require  | by the Examining Committee<br>ement for the Doctor of Philosophy<br>and Computer Engineering at the December 2009 |

| Thesis Committee:       | Sudhakar M. Reddy, Thesis Supervisor                                                                              |

|                         | Sreejit Chakravarty, Thesis Supervisor                                                                            |

|                         | Jon G. Kuhl                                                                                                       |

|                         | Karl E. Lonngren                                                                                                  |

|                         | Zhiqiang Liu                                                                                                      |

|                         | Hantao Zhang                                                                                                      |

To My Family

#### **ACKNOWLEDGMENTS**

First and foremost I would like to express my sincere gratitude to my thesis supervisor Professor Sudhakar M. Reddy for the invaluable guidance, encouragement, patience and support during the course of this research. Without his guidance this work would not have been possible. I am always inspired by his enthusiasm for pursuing best quality work. Equal amount of thanks are given to my advisor Dr. Sreejit Chakravarty of LSI Corporation for suggesting the research topic of this thesis, his constructive advices and mentoring throughout this research. Thanks are also due to Professor Jon Kuhl, Professor Karl Lonngren, Professor John Robinson, Professor Zhiqiang Liu and Professor Hantao Zhang for serving on my doctoral committee.

I would also like to thank LSI Corporation and Semiconductor Research Corporation for providing me an excellent research environment and financial support through grant 2007-TJ-1583. I especially like to thank Arun Gunda and Prabhu Krishnamurthy of LSI Corporation for their support and giving me the opportunity to work in an industrial environment.

My sincere thanks are also given to Professor Irith Pomeranz of Purdue University and all my friends at University of Iowa and LSI Corporation, for their encouragement, advice and support, which made this research a pleasant and stimulating experience. In particular, I am greatly indebted to Narendra Devta-Prasanna, Cam Lu and Thai-Minh Nguyan.

Mere words are not sufficient to express my gratitude towards my parents and parents-in-law, Jinzhong Yang, Qunxian Wang, Shiyao Xie and Linghua Hu, for their unwavering encouragement, support and love throughout my life.

Finally, a very special thank goes to my dearest wife Juan Xie for her infinite love, understanding and affection especially when we were apart, for all of the joyful life she brought me and for taking good care of me and our lovely daughter Rongxi Yang.

#### **ABSTRACT**

Semiconductor industry goals for the quality of shipped products continue to get higher to satisfy customer requirements. Higher quality of shipped electronic devices can only be obtained by thorough tests of the manufactured components. Scan chains are universally used in large industrial designs in order to cost effectively test manufactured electronic devices. They contain nearly half of the logic transistors in large industrial designs. Yet, faults in the scan cells are not directly targeted by the existing tests. The main objective of this thesis is to investigate the detectability of the faults internal to scan cells.

In this thesis, we analyze the detection of line stuck-at, transistor stuck-on, resistive opens and bridging faults in scan cells. Both synchronous and asynchronous scan cells are considered. We define the notion of half-speed flush test and demonstrate that such new tests increase coverage of internal faults in scan cells. A new set of flush tests is proposed and such tests are applied at higher temperatures to detect scan cell internal opens with a wider range of resistances. We also propose new scan based tests to further increase the coverage of those opens. The proposed tests are shown to achieve the maximum possible coverage of opens in transistors internal to scan cells. For an asynchronous scan cell considered, two new flush tests are added to cover the faults that are not detected by the tests for synchronous scan cells. An analysis of detection of a set of scan cell internal bridging faults is described. Both zero-resistance and nonzero-resistance bridging fault models are considered. We show that the detection of some zero-resistance non-feedback bridging faults requires two-pattern tests. We classify the undetectable faults based on the reasons for their undetectability.

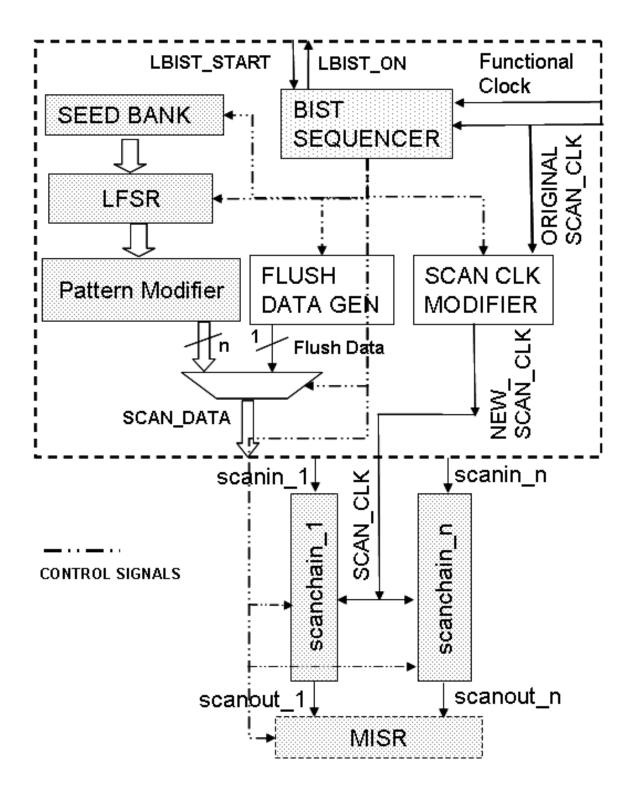

We also propose an enhanced logic BIST architecture that accomplishes the new flush tests we propose to detect scan cell internal opens.

The effectiveness of these new methods to detect scan cell internal faults is demonstrated by experimental results using some standard scan cells from a large industrial design.

# TABLE OF CONTENTS

| LIST OF T | ABLES                                                                                                                                                                                                                                                    | ix                         |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| LIST OF F | GURES                                                                                                                                                                                                                                                    | X                          |

| CHAPTER   | I INTRODUCTION                                                                                                                                                                                                                                           | 1                          |

|           | 1.1 Design-for-test and scan design                                                                                                                                                                                                                      | ∠                          |

| CHAPTER   | II REVIEW OF TESTS AND METHODS FOR TESTING OF SCAN CELL                                                                                                                                                                                                  | 7                          |

|           | 2.1 The scan cell and existing tests 2.2 Test methods for testing of scan flip-flops 2.2.1 Current testing (IDDQ testing) 2.2.2 Checking experiment method 2.3 Design-for-test methods to enhance testability of scan flip-flops 2.4 Summary and remarks | 11<br>11<br>12             |

| CHAPTER   | III ON DETECTABILITY OF SCAN CELL INTERNAL FAULTS USING STUCK-AT AND STUCK-ON FAULT MODELS                                                                                                                                                               | 20                         |

|           | 3.1 Introduction 3.2 Preliminaries 3.2.1 Stuck-at and stuck-on fault models 3.2.2 Previous related work 3.3 Half-speed flush test 3.4 Probabilistically detected faults 3.5 Experimental Results 3.5.1 Coverage gaps identified 3.6 Conclusions          | 22<br>23<br>24<br>26<br>27 |

| CHAPTER   | IV ANALYSIS OF DETECTABILITY OF INTERNAL BRIDGING FAULTS IN SCAN CELL  4.1 Introduction 4.2 Preliminaries 4.2.1 Bridging fault model 4.2.2 Faults and tests analyzed 4.3 Non-feedback zero-resistance bridging faults requiring two pattern tests        | 36<br>38<br>38             |

|           | 4.4 Detection with half-speed flush test 4.5 Experimental results 4.5.1 Undetectable faults analysis 4.5.2 Resistive bridging faults 4.5.3 Design for test to address undetectable bridging faults 4.6 Conclusions                                       | 44<br>45<br>46<br>47       |

|                | EW TESTS FOR DETECTION OF INTERNAL LARGE                                                    |                |

|----------------|---------------------------------------------------------------------------------------------|----------------|

| RES            | ISTANCE STUCK-OPEN FAULTS IN SCAN CHAIN                                                     | 53             |

| 5 1 1          |                                                                                             | <b>5</b> 0     |

| 5.1 I          | IntroductionPreliminaries                                                                   | 5 <i>5</i>     |

|                | 5.2.1 Stuck-open fault model                                                                |                |

|                | 5.2.2 Open faults studied                                                                   | 5 <del>1</del> |

| 5.3.5          | Scan stuck-open flush tests                                                                 | 57             |

|                | 5.3.1 Flush tests in the designated order                                                   | 58             |

|                | 5.3.2 Flush testing after holding the clock signal at 0 or 1 for a                          |                |

|                | duration of several clock cycles                                                            | 60             |

| ~ A .          | 5.3.3 Flush test with very slow clocks                                                      | 63             |

| 5.4 A          | ATPG generated stuck-open tests                                                             | 64             |

|                | 5.4.1 Stuck-open faults detection requiring TE = 10                                         | 03<br>67       |

| 5 5 F          | 5.4.2 Stuck-open faults detection requiring TE = 01                                         | 67             |

| 5.51           | Conclusions                                                                                 | 67<br>68       |

| 3.0 (          |                                                                                             | 00             |

| CHAPTER VI E   | ENHANCED TESTS AND METHODS FOR DETECTION OF                                                 |                |

| INT            | ERNAL RESISTIVE OPEN FAULTS IN SCAN CHAIN                                                   | 77             |

| - 1 -          |                                                                                             |                |

|                | ntroduction                                                                                 |                |

| 6.2 F          | Preliminaries                                                                               | /8<br>70       |

|                | 6.2.2 Tests and open faults considered                                                      | 19<br>82       |

|                | 6.2.3 Coverage gaps of scan stuck-open tests for resistive opens                            | 02             |

|                | 6.2.3 Coverage gaps of scan stuck-open tests for resistive opens internal to scan cell      | 85             |

| 6.3 I          | Proposed methods to improve fault coverage of resistive open faults                         | 85             |

|                | 6.3.1 Leakage current effects on the detection of faults in class 4                         | 88             |

|                | 6.3.2 Widening detectable resistance range of faults in class 6 by                          | 0.1            |

|                | slower speed flush tests                                                                    | 91             |

|                | 6.3.3 Observation on ATPG boundary TDF tests vs. flush tests in detecting faults in class 3 | 03             |

|                | Conclusions                                                                                 |                |

| 0.4 (          | Soliciusions                                                                                | ,              |

| CHAPTER VII    | AN ENHANCED LOGIC BIST ARCHITECTURE FOR ONLINE                                              |                |

| TES            | TING USING SCAN STUCK-OPEN FLUSH TESTS                                                      | 98             |

|                |                                                                                             |                |

|                | ntroduction                                                                                 |                |

|                | Preliminaries                                                                               |                |

|                | 7.2.1 BIST architectures and tests applied by Logic BIST                                    |                |

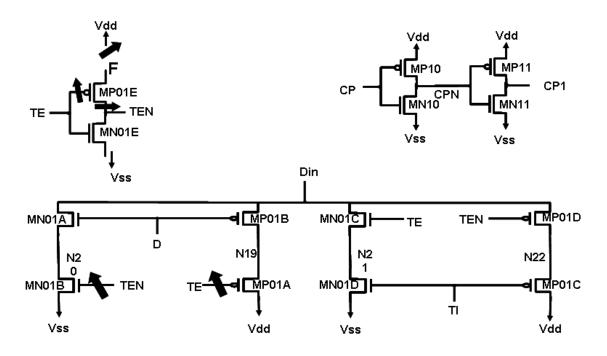

|                | Proposed enhanced logic BIST architecture                                                   |                |

| 7.4 (          | Conclusions                                                                                 | 107            |

|                |                                                                                             |                |

|                | DETECTION OF TRANSISTOR STUCK-OPEN FAULTS IN                                                |                |

| ASY            | NCHRONOUS INPUTS OF SCAN CELL                                                               | 112            |

| 011            | intuo divotion                                                                              | 110            |

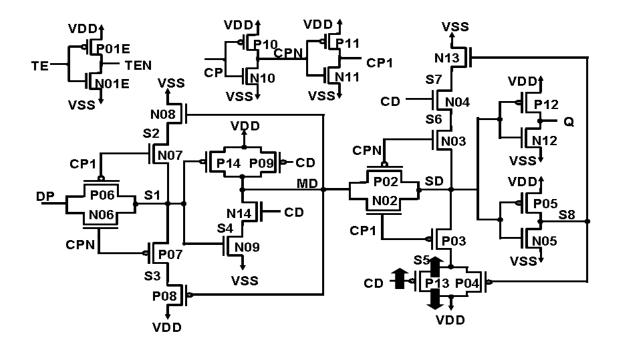

| 8.1 I          | IntroductionAsynchronous scan cell studied and faults considered                            | 112<br>112     |

| 8.2 F<br>8.3 F | Proposed flush tests                                                                        | 113<br>114     |

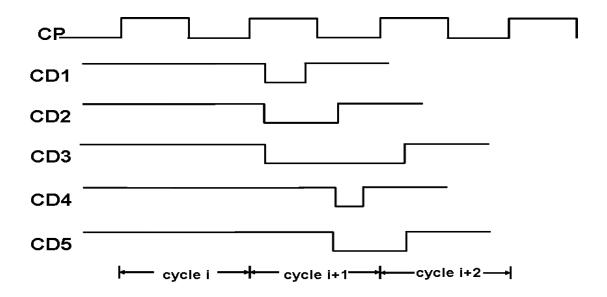

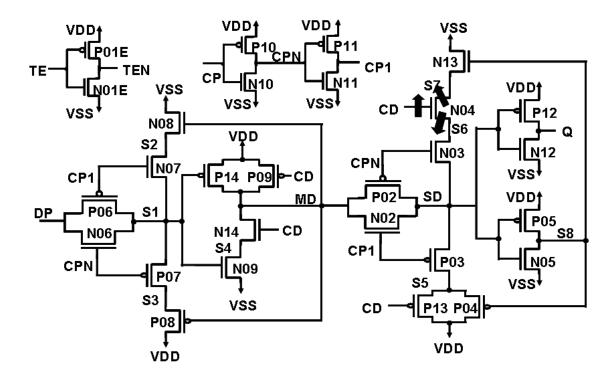

| 0.3 1          | 8.3.1 Detection of opens in transistors turned on when $CD = 0$                             | 114            |

|                | 8.3.2 Detection of opens in transistors turned on when $CD = 1$                             | 118            |

| 0.4.6          | Conclusions                                                                                 | 110            |

| CHAPTER IX CONCLUSIONS                                                                  | 125 |

|-----------------------------------------------------------------------------------------|-----|

| 9.1 Future research on further improving the test quality for scan cell internal faults | 127 |

| 9.2 Future research to generalize the test method for all types of scan cells           |     |

| 9.3 Silicon experiment and scan chain internal fault diagnosis                          |     |

| REFERENCES                                                                              | 129 |

# LIST OF TABLES

| Table 1-1: Gate and transistor data of an industrial design                                                 | 6   |

|-------------------------------------------------------------------------------------------------------------|-----|

| Table 2-1: Transition table of MD flip-flop                                                                 | 10  |

| Table 2-2: Boundary SAF/TDF list and ATPG test patterns of scan flip-flop                                   | 11  |

| Table 3-1: HSPICE simulation summary                                                                        | 30  |

| Table 3-2: Low Vdd testing of MN01C SON fault at 25°C with test: $D=0$ , $TE=0$ , $TI=1$ , $Q=0$            | 30  |

| Table 4-1: Simulation results for resistance of $10\Omega$                                                  | 49  |

| Table 4-2: Simulation results for bridge resistances of $100\Omega$ , $500\Omega$ and $1K\Omega$            | 49  |

| Table 4-3: Undetected faults for bridge resistances of $100\Omega$ , $500\Omega$ and $1K\Omega$             | 50  |

| Table 5-1: Scan stuck-open flush tests                                                                      | 58  |

| Table 5-2: Additional stuck-open ATPG tests                                                                 | 65  |

| Table 5-3: Experiment summary of stuck-open faults detected                                                 | 69  |

| Table 6-1: Scan stuck-open flush tests proposed in Chapter V                                                | 84  |

| Table 6-2: Fault coverage of the stuck-open tests to detect resistive opens at 25 °C                        | 85  |

| Table 6-3: Scan resistive stuck-open flush tests proposed                                                   | 87  |

| Table 6-4: Fault coverage by applying the proposed tests at higher temperatures                             | 87  |

| Table 6-5: Simulation results for MP03 drain open at 25°C, 50°C, 75°C, 100°C and 125°C                      | 91  |

| Table 6-6: Applying the tests in Table 6-1 and Table 6-3 to MN06 drain open fault                           | 93  |

| Table 6-7: Appling ATPG TDF test at 1GHz to the fault in class 3 for variable slacks of combinational logic | 95  |

| Table 7-1: Scan resistive stuck-open flush tests proposed in Chapter VI                                     | 108 |

| Table 7-2: Additional scan based tests described in Chapter V                                               | 108 |

| Table 7-3: Parameter for BIST_SEQUENCER                                                                     | 108 |

| Table 8-1: Summary of the transistor SOPs considered                                                        | 114 |

### LIST OF FIGURES

| Figure 1-1: Scan design process                                | 3  |

|----------------------------------------------------------------|----|

| Figure 2-1: Scan flip-flop implementation                      | 9  |

| Figure 2-2: Gate level and ATPG library models for a scan cell | 10 |

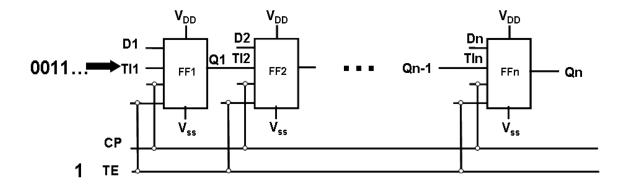

| Figure 2-3: Application of flush test 00110011 to a scan chain | 10 |

| Figure 2-4: Open fault turns scan cell into dynamic state      | 15 |

| Figure 2-5: D-latch used and proposed in [2.2]                 | 16 |

| Figure 2-6: Undetected stuck-open faults (SOPs) in Figure 2-1  | 17 |

| Figure 2-7: Clocked inverters used                             | 18 |

| Figure 3-1: Stuck-at fault model                               | 31 |

| Figure 3-2: Scan cell used in [3.8]                            | 31 |

| Figure 3-3: Fault CP1 stuck-at-0.                              | 32 |

| Figure 3-4: Detection of the fault CP1 stuck-at-0              | 33 |

| Figure 3-5: Logic diagram of a scan chain with length 3        | 33 |

| Figure 3-6: Detection of CP1 stuck-at-0 with S = T             | 34 |

| Figure 3-7: Detection of CP1 stuck-at-0 with S = 2T            | 34 |

| Figure 3-8: IDDQ testing of MN01C SON                          | 35 |

| Figure 4-1: Negligible resistance bridging fault models        | 39 |

| Figure 4-2: Resistive bridging fault behavior                  | 41 |

| Figure 4-3: Bridging fault D-CPN                               | 50 |

| Figure 4-4: Detection of fault D-CPN with two-pattern test     | 51 |

| Figure 4-5: Bridging fault DP-N1                               | 51 |

| Figure 4-6: Undetected bridging fault N4-Q                     | 52 |

| Figure 4-7: Bridging fault DP-D                                | 52 |

| Figure 5-1: Transistor stuck-open fault model                  | 69 |

| Figure 5-2: Stuck-open at gate of transistor.                  | 69 |

| Figure 5-3: IDDQ detectable floating gate defects                           | 70  |

|-----------------------------------------------------------------------------|-----|

| Figure 5-4: Large resistance stuck-open fault model considered in Chapter V | 70  |

| Figure 5-5: Gate of transistor MP05 and MP12 stuck-open                     | 71  |

| Figure 5-6: Detection of transistor MP05 gate stuck-open                    | 71  |

| Figure 5-7: Gate of transistor MN02 stuck-open                              | 72  |

| Figure 5-8: Detection of transistor MN02 gate stuck-open                    | 72  |

| Figure 5-9: Gate of transistor MN06 stuck-open                              | 73  |

| Figure 5-10: Detection of transistor MN06 gate stuck-open                   | 73  |

| Figure 5-11: SOP on drain/source of transistor MP08                         | 74  |

| Figure 5-12: SOPs detected by ATPG test with TE = 10                        | 74  |

| Figure 5-13: Detection of SOP on drain/source of MP01E                      | 75  |

| Figure 5-14: Logic diagram of a scan chain with length 3                    | 75  |

| Figure 5-15: SOPs detected by ATPG test with TE = 01                        | 76  |

| Figure 5-16: Undetected stuck-open faults                                   | 76  |

| Figure 6-1: Resistive stuck-open fault model                                | 84  |

| Figure 6-2: Classification of transistor open faults                        | 84  |

| Figure 6-3: Logic diagram of a scan chain with length 3                     | 87  |

| Figure 6-4: SOP on drain/source of transistor MP03                          | 90  |

| Figure 6-5: Gate of transistor MN06 stuck-open                              | 95  |

| Figure 6-6: Detection of transistor MN06 gate SOP                           | 96  |

| Figure 6-7: Drain of transistor MNE stuck-open                              | 96  |

| Figure 6-8: Detection of transistor MNE drain SOP                           | 97  |

| Figure 7-1: Logic BIST Structures                                           | 101 |

| Figure 7-2: Scan testing with flush test 00110011                           | 102 |

| Figure 7-3: Enhanced logic BIST architecture proposed                       | 109 |

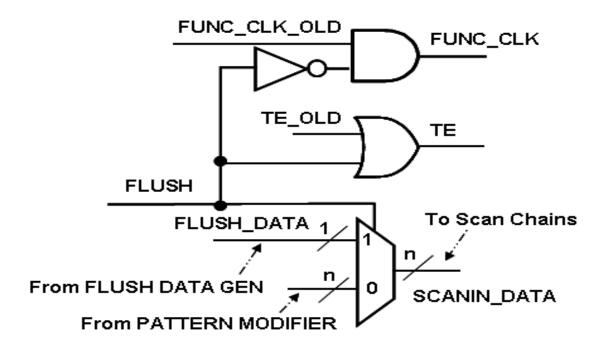

| Figure 7-4: SCAN_DATA MUX and TE, FUNC_CLK generation                       | 110 |

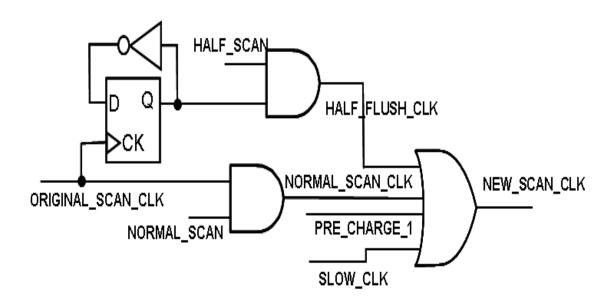

| Figure 7-5: A realization of SCAN CLK MODIFIER                              | 110 |

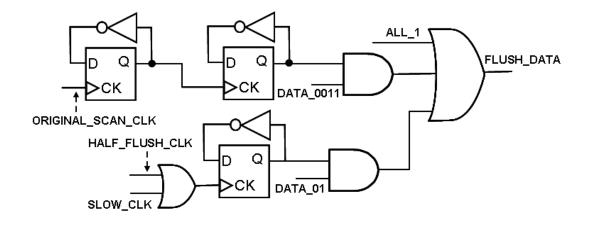

| Figure 7-6: An implementation of FLUSH_DATA_GEN               | 111 |

|---------------------------------------------------------------|-----|

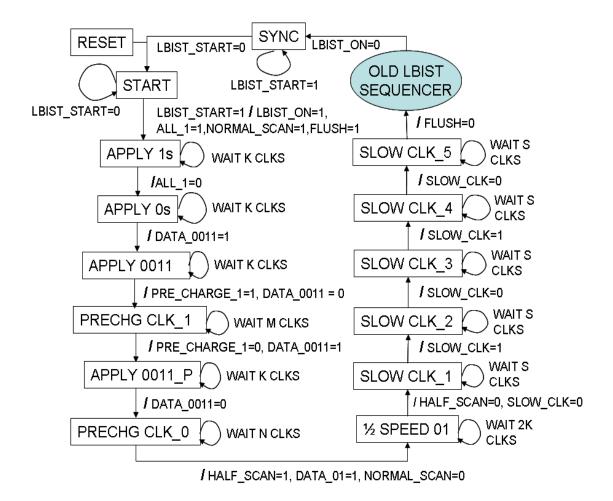

| Figure 7-7: A definition of the BIST SEQUENCER                | 111 |

| Figure 8-1: Scan cell with asynchronous reset input CD        | 120 |

| Figure 8-2: SOPs in transistor P09                            | 121 |

| Figure 8-3: Detection of SOPs in transistor P09               | 121 |

| Figure 8-4: SOPs in transistor P13                            | 122 |

| Figure 8-5: Detection of SOPs in transistor P13               | 122 |

| Figure 8-6: Cases of CD reset in functional mode of operation | 123 |

| Figure 8-7: SOPs in transistor N14                            | 123 |

| Figure 8-8: SOPs in transistor N04                            | 124 |

#### CHAPTER I INTRODUCTION

Semiconductor industry goals for the quality of shipped products continue to get higher to satisfy customer requirements. For example high end automobile manufacturers are requiring zero defects in the electronic components. Similar requirements are customary for life critical systems. Higher quality of shipped electronic devices can only be obtained by thorough tests of the manufactured components. **Testing** of Very Large Scale Integrated (VLSI) circuits is an experiment in which the circuits are exercised by a group of binary values to ascertain the correctness of circuit behaviors.

#### 1.1 Design-for-test and scan design

Test complexity can be converted into costs associated with the testing process. It may be from the cost of test pattern generation, the cost of fault simulation and generation of fault location information, the cost of test equipment, and the cost related to the testing process itself called the time required to detect a fault [1.1]. **Testability** is a design characteristic that influences various costs associated with testing. **Design for testability** or design-for-test (DFT) methods are design efforts specifically employed to ensure that a device is testable.

Testable circuitry is both controllable and observable. The **controllability** is used to measure the difficulty of setting a line to a value. In order for the detection of a fault, fault propagation is required where primary inputs are set to appropriate values such that the fault is able to propagate to at least one of the primary outputs (i.e., one or more primary outputs present the faulty value due to the fault). The ability of fault propagation is measured by the **observability** which indicates the relative difficulty of propagating an error from a line to a primary output. In a testable design, setting specific values on the primary inputs results in values on the primary outputs which indicate whether or not the internal circuitry works properly.

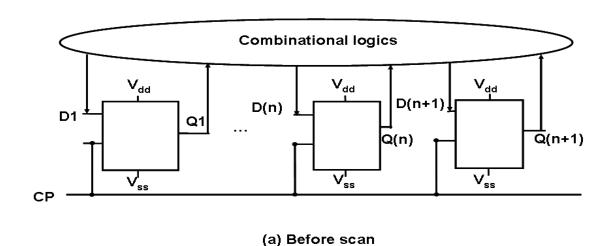

The most common DFT technique to increase the controllability and observability of a circuit is **scan design**, which modifies the internal sequential circuitry of the design. The digital circuits are classified into combinational logic and sequential logic. **Combinational circuit** outputs depend solely on the primary inputs, whereas **sequential circuit** outputs depend on stored values from previous time frame also the primary inputs. The goal of scan design is to make difficult-to-test sequential circuit behave like an easier-to-test combinational circuit during the testing process. In order to achieve this goal sequential elements are replaced with so called scan cells. These scan cells are then stitched together into scan chains. This process is demonstrated next refer to Figure 1-1.

The design shown in Figure 1-1 contains both combinational and sequential portions. In Figure 1-1(a), the values of functional data-in (Ds) in the memory elements are the state outputs from the combinational logic. These values are then transferred to Qs which are the inputs of the combinational logic in the next time frame. To initialize the states of the circuit in Figure 1-1(a) we may need back-tracking the states of the previous time frames. In addition, it may also require line justifications to propagate the errors. Hence, this "Before scan" circuit is difficult to initialize to a known state, making it difficult to both control the internal circuitry and observe its behavior using the primary inputs and outputs of the design. However, we may add the scan circuitry into the design to set the state variables and observe the state outputs directly.

Figure 1-1(b) has two additional inputs, scan-in (TI1) and scan enable (TE), and one additional output, Q(n+1). The scan cells replace the original memory elements so that scan data are shifted into the combinational logic from TI1 signal when TE is active. During the functional mode (normal operation), TE is deactivated. No values are read in from TIs in scan cells. Ds are selected to propagate to Qs. During the testing, the operating procedure is as follows:

Enable the scan enable signal TE to allow shifting to initialize scan cells.

This will load TIs with proper values.

- (2) Turn off the scan clocks and apply primary inputs to the circuitry. The primary outputs and new values on Ds are set after this step.

- (3) Pulse the clock to capture new values into scan cells.

- (4) Finally, activate the TE signal to shift Qs out of the scan chain. The values at Q(n+1) are then compared with the expected values.

In the scan design, we can set input states and primary inputs. Besides, both state outputs and primary output are observed.

Combinational logics  $V_{\rm dd}$  $V_{dd}$  $V_{dd}$ D(n+1) D(n) D1 Q1 Flip-flop TI(n) Flip-flop Flip-flop Q(n+1) Q(n)  $\overline{V}_{\!\!\!\!\!s\underline{s}}$  $V_{ss}^{I}$  $V_{ss}^{I}$ ΤE (b) Scan cells inserted

Figure 1-1: Scan design process

#### 1.2 Overview of the thesis

Because of the rapid increase in the complexity of VLSI circuitry, the issue of testing and design-for-test are becoming increasingly more important. In order to cost effectively test manufactured electronic devices, scan design is universally used in industry. In full scan designs, all flip-flops in the logic part of a design are grouped into the scan chains that facilitate loading tests applied to detect defects as well as observing the circuit response to the tests. This requires augmenting the functional flip-flops into what are called scan flip-flops or scan cells. Even though the main purpose of scan cells is to facilitate loading tests and unloading test responses, faults in scan cells may affect functional operation if left undetected. This is because scan cells contain the functional flip-flops. The undetected faults in scan cells may also affect long term reliability of shipped products. Table 1-1 shows the gate and transistor counts of a 90nm industrial design we investigated. Approximately 14.3% of the logic cells are scan cells but they contain about 43.6% of the total number of transistors in the logic part of the design. Nevertheless, faults in the scan cells are not directly targeted and assumed detected by what are called flush tests. Thus, it is important to determine the coverage of faults internal to the scan cells and investigate cost effective methods to augment tests generated by standard automatic test pattern generation (ATPG) procedures to detect scan cell internal faults.

The assumptions made to represent the nature of logic faults are called **fault models**. Traditional fault models include stuck-at, stuck-on, stuck-open and bridging faults. In this thesis, we investigate the detectability of stuck-at, transistor stuck-on, transistor opens and shorts internal to scan cells by the existing tests which include flush tests and ATPG tool generated tests. This thesis investigates to develop new tests and methodologies to apply the tests to maximize the fault coverage.

### 1.3 Organization of the thesis

The rest of this thesis is organized in the following manner.

Chapter II gives an introduction of the structure of scan flip-flop and briefly reviews of the existing tests and some related previous work for testing of scan cells.

Chapter III presents results of the first step in the direction of investigating the use of standard scan cells and existing methods of generation and application of scan based tests to detect scan cell internal faults using stuck-at and stuck-on fault models. A new flush test, half-speed flush test, is proposed to enhance the detectability of those considered faults.

Chapter IV reports the detection of a set of scan cell internal bridging faults extracted from layout. A comprehensive analysis of bridging faults internal to scan cell is developed.

The detectability of large resistance opens in transistors internal to scan cells is investigated in Chapter V. New flush tests to maximize the fault coverage of those opens in a synchronous scan cell are described.

Chapter VI investigates the scan chain internal transistor opens with moderate resistances. The flush tests proposed earlier for the detection of large resistance opens internal to scan cells are modified to maximize the range of detectable open resistances. Application of flush tests at higher temperature to improve the range of open resistances detected is also discussed.

Chapter VII presents an enhanced logic BIST architecture for online testing. The new flush tests for opens internal to scan chains are augmented into the tests generated by the new logic BIST architecture.

In addition to synchronous scan cell considered, in Chapter VIII, an asynchronous scan cell is also studied and two new flush tests are added to cover the faults that are not detected by the tests for synchronous scan cell.

Finally, Chapter IX summarizes this thesis and describes some topics for future research.

Table 1-1: Gate and transistor data of an industrial design

|                            | Combinational Gate  | Latch           | Scan Flip-Flop      |

|----------------------------|---------------------|-----------------|---------------------|

| # of Cells 3678245 (85.6%) |                     | 3256<br>(0.08%) | 614159<br>(14.3%)   |

| # of Transistors           | 30634354<br>(56.4%) | 53588<br>(0.1%) | 23670019<br>(43.5%) |

# CHAPTER II REVIEW OF TESTS AND METHODS FOR TESTING OF SCAN CELL

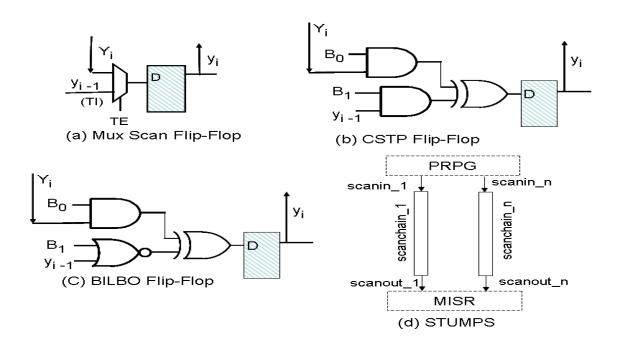

In this chapter we summarize the previous works on testing of scan cells. Specifically, in the first part we introduce the structure of scan cell using a standard scan flip-flop from industrial design and discuss the existing tests for testing scan chains. Generally speaking, testing methods in order to enhance the testability of scan cells can be classified into two major types. One is to develop testing methods to generate tests other than the existing tests and the other is to change the design of the scan cell such that the internal faults are detected by the existing tests. The second part of this chapter reviews some test methods for scan cell internal faults. In the last part, we introduce some design for test methods to enhance the testability of scan cells. Finally, Section 2.4 summarizes this chapter.

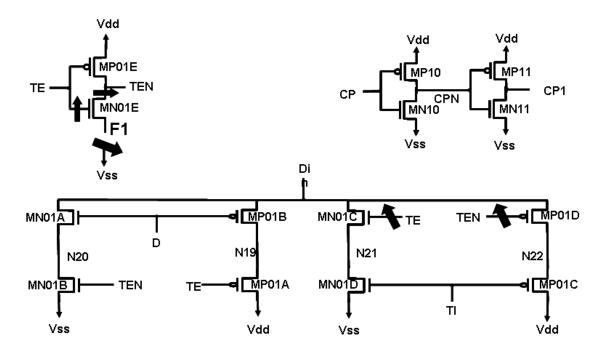

## 2.1 The scan cell and existing tests

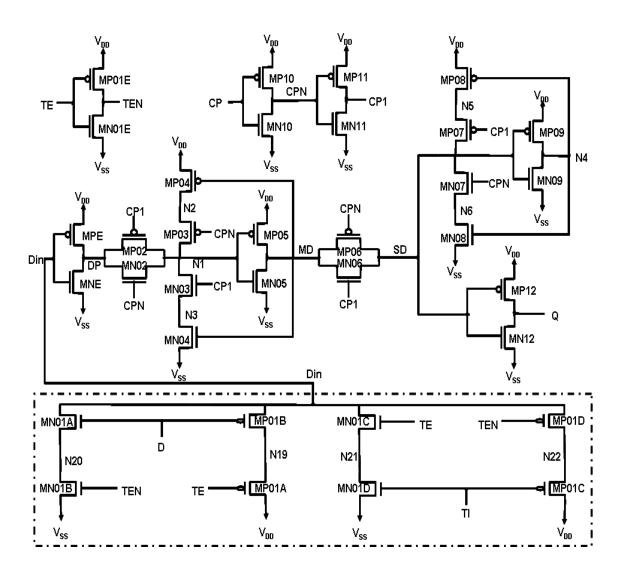

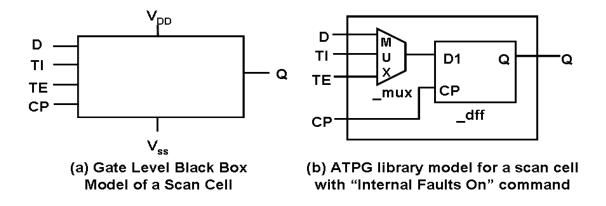

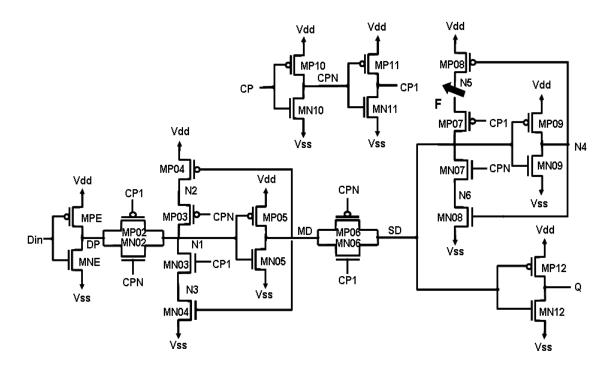

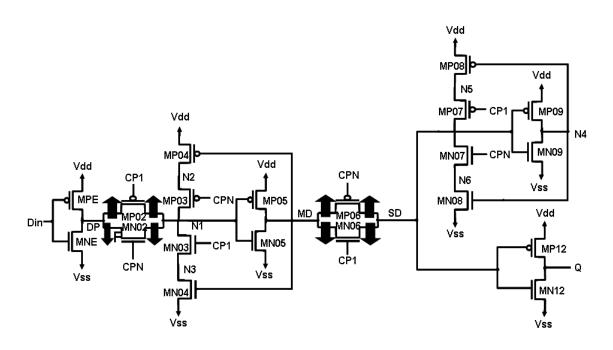

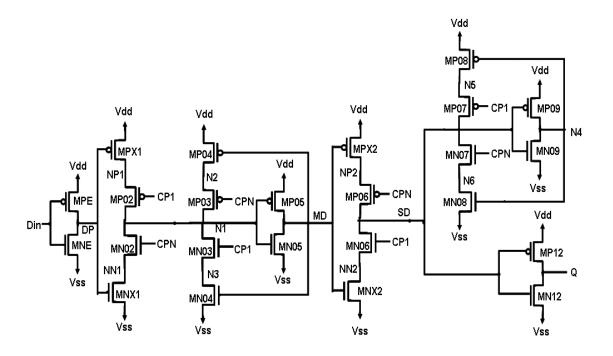

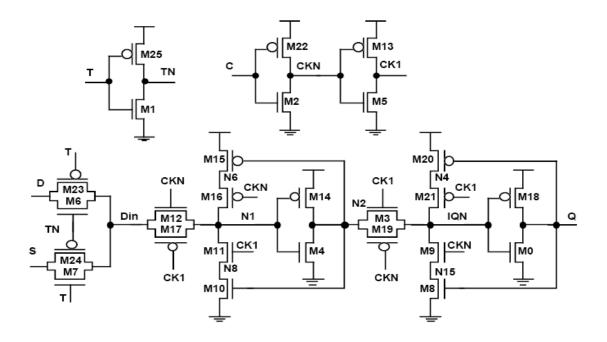

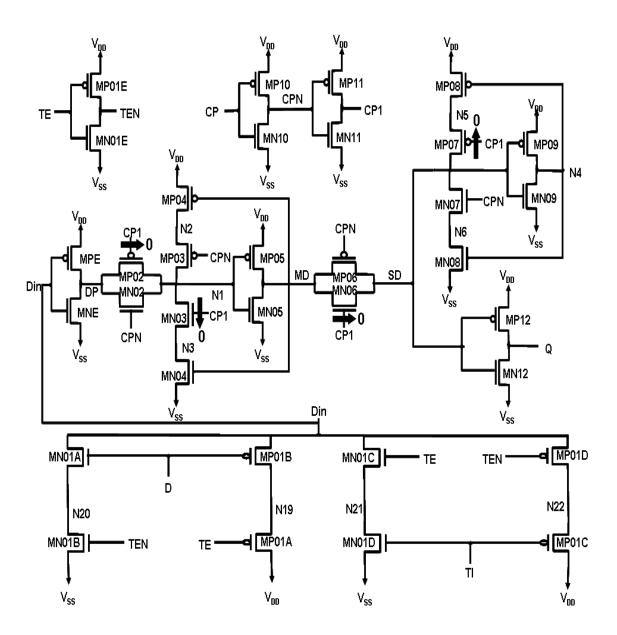

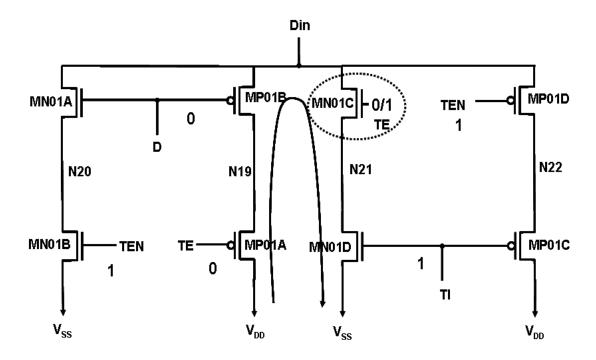

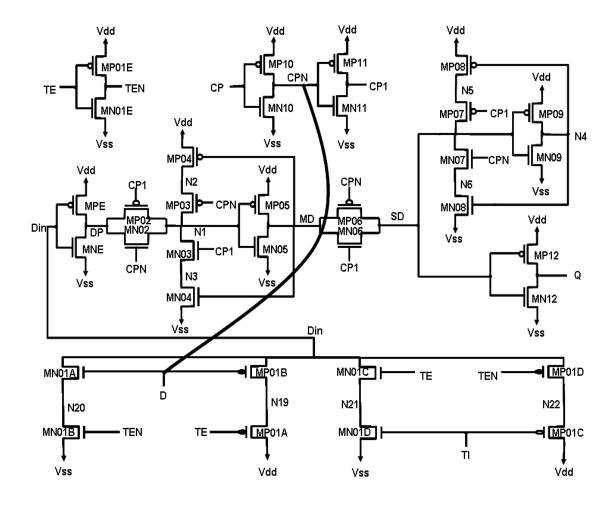

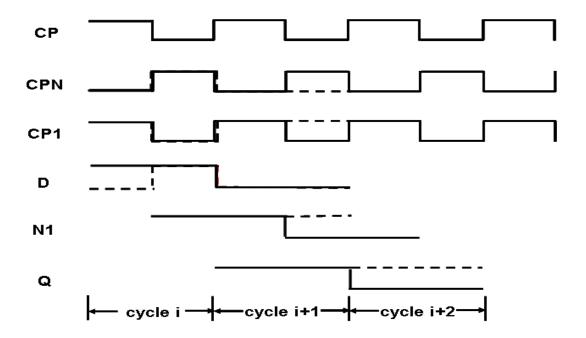

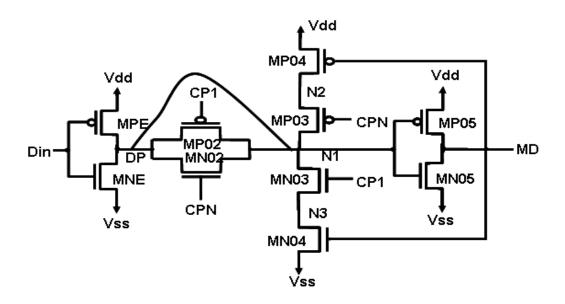

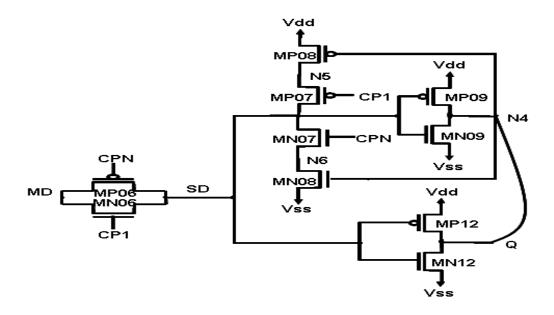

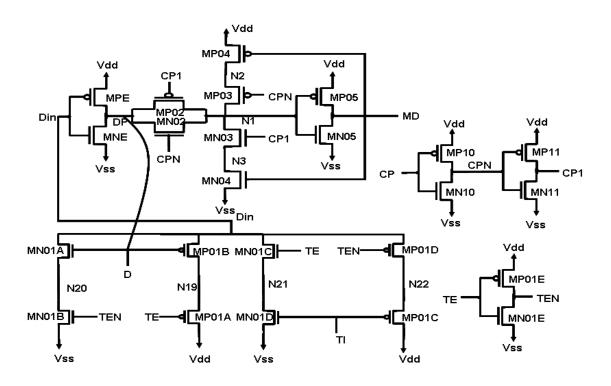

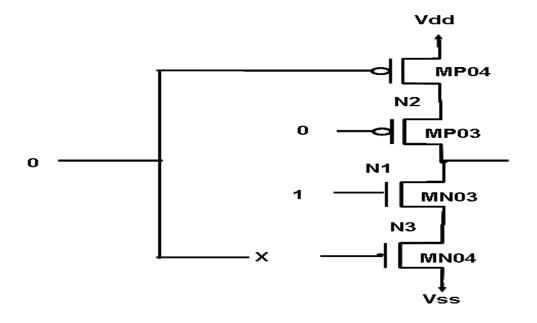

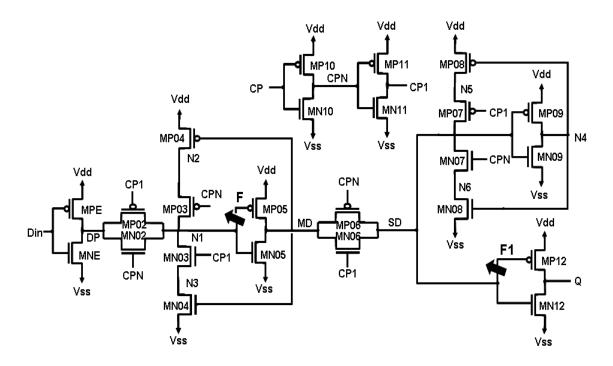

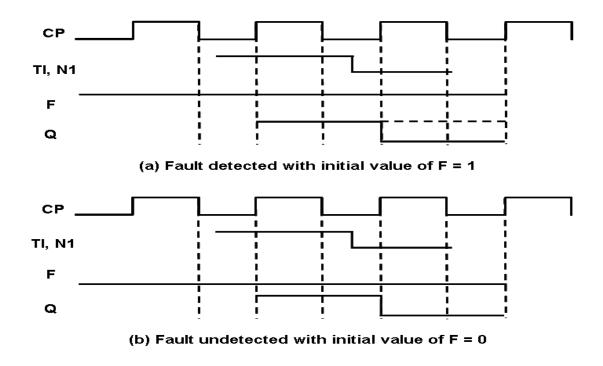

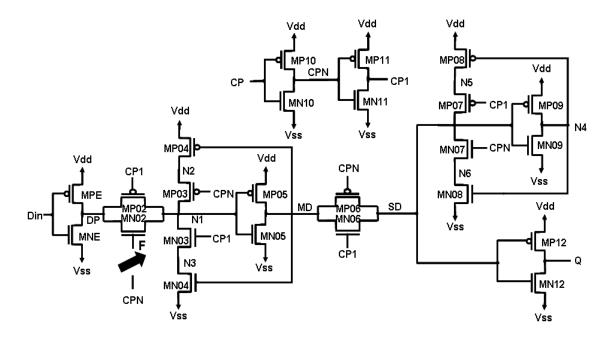

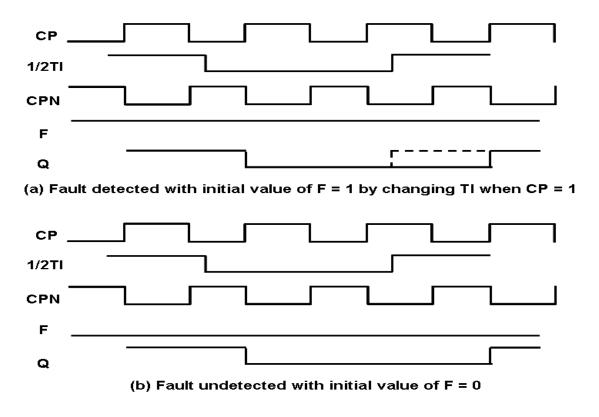

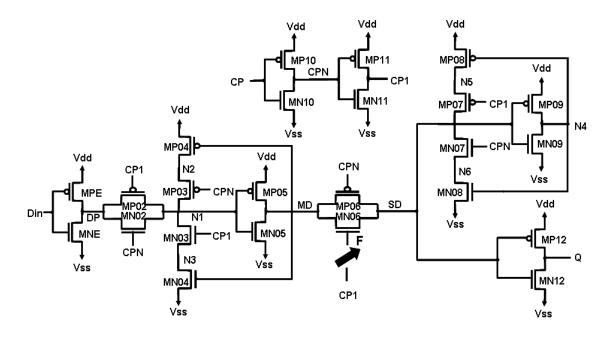

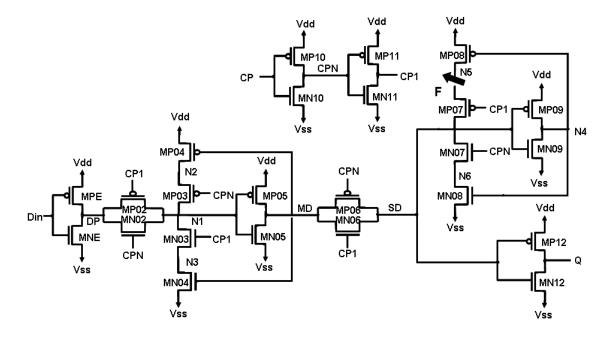

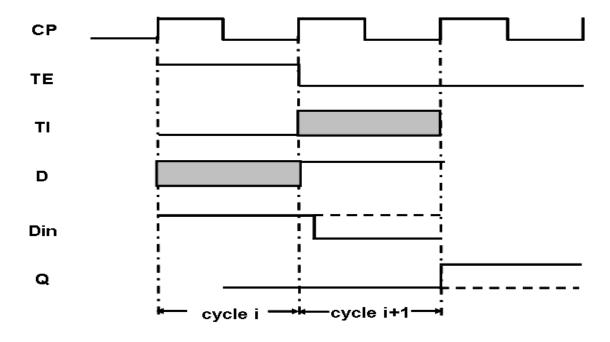

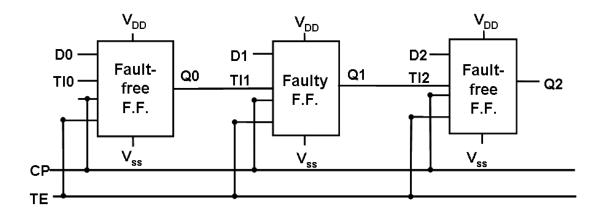

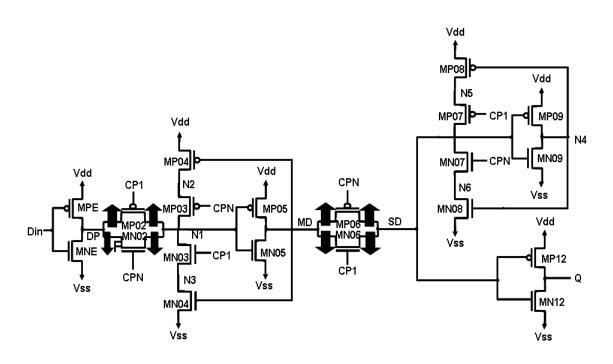

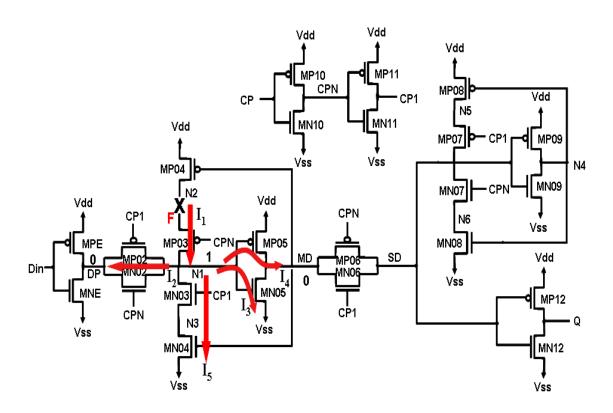

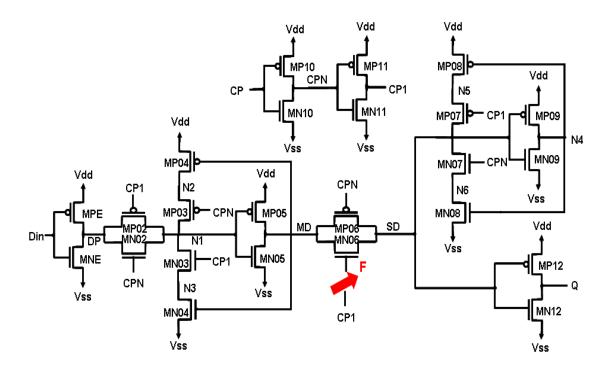

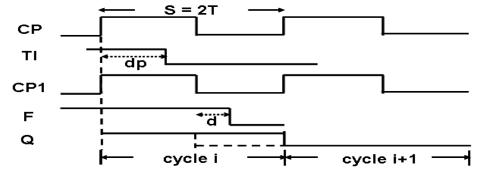

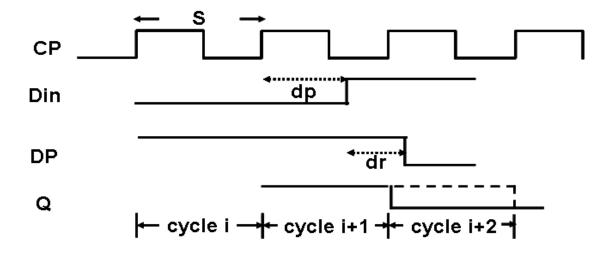

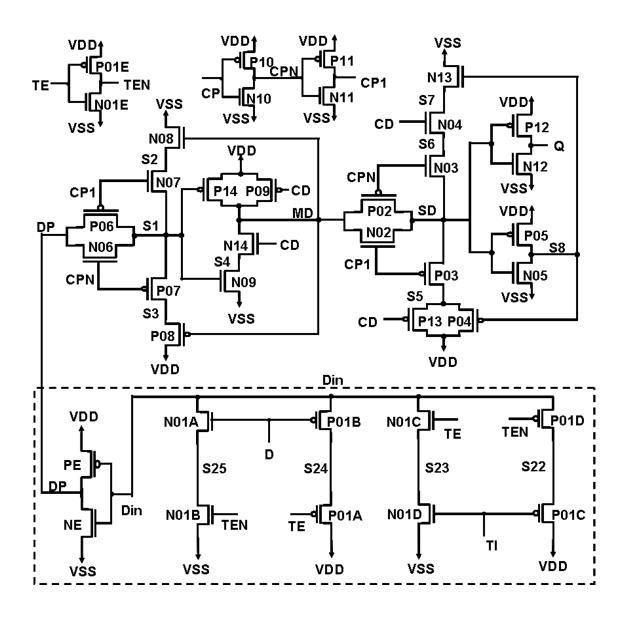

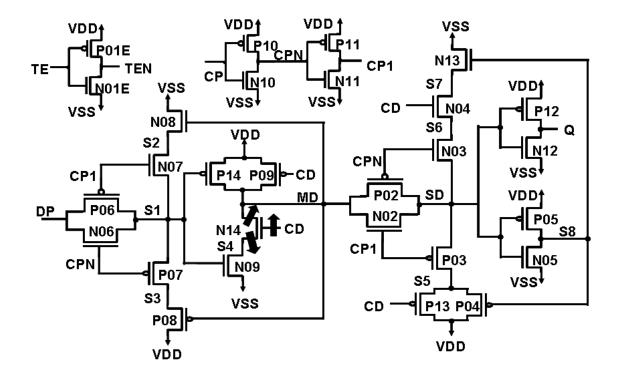

There are various flip-flop structures even for the same type of flip-flop. However, they operate in a similar manner and are obtained by cascading two latches each showing input logic values at one of the two clock phases (clock = 1 and clock = 0). One of a scan cell implementation is shown in Figure 2-1. It is a positive edge triggered Muxed input D flip-flop (MD flip-flop) whose transition table is given in Table 2-1. The circuit highlighted by the dashed rectangle is the multiplexer used for selecting between the functional data-in (D) and test scan-in (TI) inputs. The circuit between the nodes DP and MD is the master latch of the flip-flop and this is connected to the slave latch, the circuit between the node MD and the output (Q). When the test enable signal (TE) is set to 1 (0), TI (D) is selected. The value of TI (D) then propagates into the master latch when clock (CP) is low. Meanwhile, the nodes in the slave latch retain the values from the previous clock cycle. When CP turns to high, the signal stored in the master latch propagates into the slave latch and to the output of the scan cell.

The existing ATPG tools model scan flip-flops in scan chains as black boxes shown in Figure 2-2(a) and generate tests for faults at inputs and outputs of the scan flipflops. The tests generated by ATPG targeting stuck-at and transition delay faults at data input (D) and output (Q) are called boundary SAF/TDF tests shown in Table 2-2 in this thesis. The test procedures are described as follows. The logic values required at the scan input (TI) of all scan cells are shifted into the scan chain with TE = 1 for n clock cycles (n is the number of scan cells in the scan chain). Then TE is toggled to 0 for one or more cycles so that the appropriate values will apply to the combinational logics, present at D inputs and finally propagate to the outputs of scan cells. The outputs of scan cells are shifted out for another n clock cycles to compare with the expected values thereafter. "Internal Faults On" command is an option often found in commercial ATPG tools. If the "Internal Faults On" command is used for the scan cell shown in Figure 2-2(a) the ATPG library model for the scan flip-flop used will be the one in Figure 2-2(b). However, this model still hides the transistor level implementation of the scan flip-flop. Thus, no additional test patterns are generated using "Internal Faults On" command. In addition, stuck-at faults (SAFs) and transition delay faults (TDFs) for both gate level and ATPG library models are equivalent and results in the same test patterns. Therefore, "Internal Faults On" option does not improve the coverage of internal faults of the scan cells.

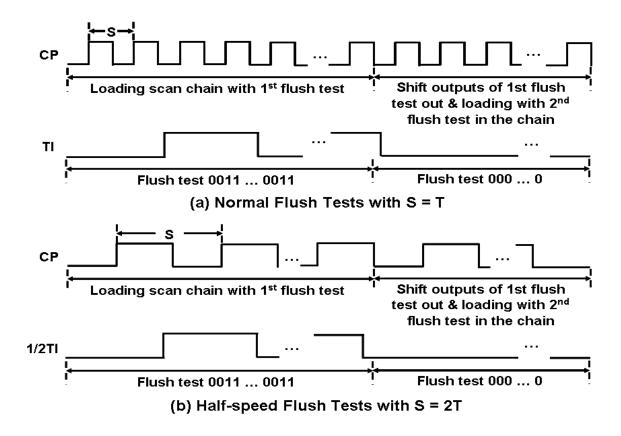

In addition to the ATPG tests targeting D and Q, faults on TE, TI and CP and faults residing in the scan cell are assumed to be detected by what are called flush tests. The flush tests are used to ascertain the integrity of scan chains. Typically used flush tests are all zeros (00...0), all ones (11...1) and 0011 sequence repeated over the length of a scan chain (00110011...). The flush tests are scanned in and out of the scan chains with scan enable active (TE = 1) throughout the application of the flush tests. Figure 2-3 shows that the flush test 00110011... is applied to a scan chain with the length of n. The sequence 0011 is scanned in and out of the scan chain with test enable signal TE = 1 in Figure 2-3. The output is observed at the output Qn and compared with the expected

value. Obviously, faults in the circuit elements internal to the scan cells are not directly targeted during the flush tests. In the sequel, flush tests and ATPG boundary SAF/TDF tests are referred to as existing tests. Earlier works, [2.1-2.8], showed that existing tests miss many internal faults.

Figure 2-1: Scan flip-flop implementation

Figure 2-2: Gate level and ATPG library models for a scan cell

Figure 2-3: Application of flush test 00110011... to a scan chain

| D | TI | TE | СР       | Q |

|---|----|----|----------|---|

| 0 | X  | 0  | <b>↑</b> | 0 |

| 1 | X  | 0  | 1        | 1 |

| X | 0  | 1  | 1        | 0 |

| X | 1  | 1  | <b>↑</b> | 1 |

Table 2-1: Transition table of MD flip-flop

Table 2-2: Boundary SAF/TDF list and ATPG test patterns of scan flip-flop

| Faults         | Test Pattern                             |

|----------------|------------------------------------------|

| D stuck-at-0   | D = 1, $TE = 0$ , $TI = X$ , $Q = 1$     |

| D stuck-at-1   | D = 0, $TE = 0$ , $TI = X$ , $Q = 0$     |

| Q stuck-at-0   | D = 1, $TE = 0$ , $TI = X$ , $Q = 1$     |

| Q stuck-at-1   | D = 0, $TE = 0$ , $TI = X$ , $Q = 0$     |

| D slow-to-rise | D = 01, $TE = 00$ , $TI = XX$ , $Q = 01$ |

| D slow-to-fall | D = 10, $TE = 00$ , $TI = XX$ , $Q = 10$ |

| Q slow-to-rise | D = 01, $TE = 00$ , $TI = XX$ , $Q = 01$ |

| Q slow-to-fall | D = 10, $TE = 00$ , $TI = XX$ , $Q = 10$ |

#### 2.2 Test methods for testing of scan flip-flops

In this section, some previous works of test methodologies for detection of scan cell internal faults are reviewed. We first introduce a testing method relies on measuring the supply current in the quiescent state (when the circuit is not switching and inputs are held at static values). Then a method that models the scan flip-flop as a state machine and generates tests using the developed state tables is discussed.

#### 2.2.1 Current testing (IDDQ testing)

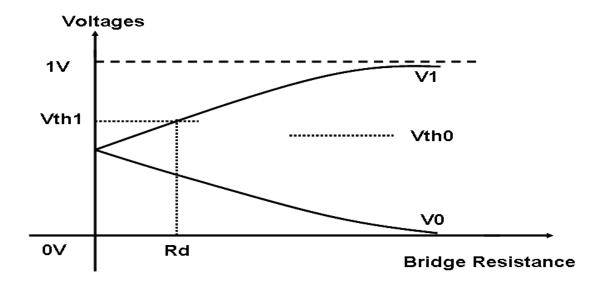

In a fault-free quiescent CMOS digital circuit, there is no static current flowing from power supply to ground assuming leakage current is negligible. This is because under normal conditions, only gates of field effect transistors (FETs) are connected to the power supply (Vdd) or ground (Vss), and gates are highly insulated preventing DC current flow. Conducting paths from Vdd to Vss only exist during switching. Hence, the measured current in defect free circuit is small. However, many semiconductor manufacturing defects cause the current in the faulty circuit to increase by orders of

magnitude, which can be easily detected and differentiated from leakage currents. The testing method of measuring power supply current in the quiescent state of defective chips is called **current testing** or **IDDQ testing**. This method has the advantage of checking the tested circuit for many faults with one measurement. In addition, IDDQ testing is easier than voltage based methods in terms of generating the tests since IDDQ test vectors require only controllability and not observability. This is because the measurement is observed through shared power supply (Vdd).

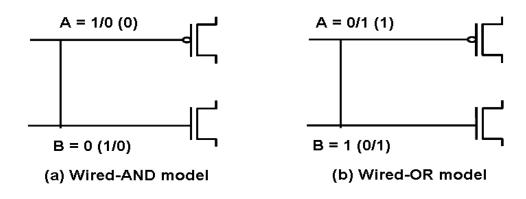

For example, short which is usually modelled by bridging fault model is a common defect frequently presents in CMOS integrated circuits. To detect such fault, the two bridged nodes are set to opposite values. It has been shown when the bridge resistance increases above some resistance both faulty nodes will behave as in the fault-free circuit. However, the current flowing from one bridged node to the other node still presents even though it is weaker with increased bridge resistances. Therefore, in addition to the voltage based test methods IDDQ testing is one option to detect resistive bridging fault. [2.8] showed that IDDQ tests can detect many faults in scan flip-flops and latches not detected by the voltage-based tests.

As we mentioned earlier the capability of tester to sense the excess current is the key in this method. However, it may lead to higher start-up costs such as current sensor circuit design is required. In addition, as the new technologies continue to shrink the feature sizes of integrated circuits, the leakage current will not be neglected. Therefore, defining the "cut-off" current value to determine faulty IDDQ will be non-trivial.

#### 2.2.2 Checking experiment method

The scan flip-flop has the structure with two latches cascaded where the operation involves the inputs changes during two clock phases (clock = 0 and clock = 1). In order to accomplish this in the testing, one can generate the test patterns that cover all possible inputs transitions from one clock phase to the other. In [2.4-2.8], Makar and McCluskey

proposed a checking sequence based tests set derivation procedures for testing faults internal to bistable elements (latches or flip-flops). The flip-flop is modeled as a state machine. It generates test for all transitions to the tested cell. In addition, both voltage-based method and IDDQ testing method are applied in the simulation results. **Checking experiment** is an input-output sequence that distinguishes a given state machine from all other state machines with the same inputs and outputs, and the same number of or fewer states [2.4].

The first step of the method is to create a primitive state table for the tested latch or flip-flop. The state table is developed based on the primary inputs and outputs. For the scan cell of Figure 2-1 which has 4 inputs and 1 output, there are 32 states. The primitive state table may be reduced from the operation limitations of inputs or operation assumptions. For example, it may assume that the value of scan-in (TI) can only change when CP = 1. Then the state transition from "CP = 0, TI = 0, TE = 1, D = 1" to "CP = 0, TI = 1, TE = 1, TE = 1, TE = 1, TE = 1 and TE = 1 is not allowed and can be deleted from the original state table. In the next step, a set of sub-sequences identify each state is derived. Finally, test patterns for all sub-sequences are defined.

The advantage of this method is that the test generation procedure does not require the internal implementation (circuit in transistor level) of the cell since the scan cell is modeled as a state machine. Hence, it is independent of scan flip-flop implementations. However, the checking sequence based method requires sequential ATPG procedures even for the circuit with full scan. In addition, it generates a large number of tests. The average size of the resulting tests, for ISCAS circuits, is 4.5 times the size of a single stuck-at test set which is a barrier to its use in practice. Since the checking sequence based method is a functional tests generation procedure, it needs to modify the existing ATPG which is expensive.

### 2.3 Design-for-test methods to enhance testability of scan

#### flip-flops

In this section we give a brief review of design for test methods to enhance the testability of scan cells.

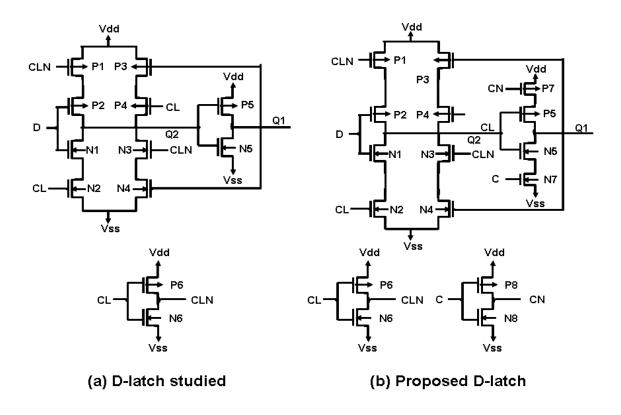

Many open defects affecting functional mode of operation of scan cells are hard to detect. Some of them in the transistors internal to scan cell may turn the scan flip-flop from a static state to a dynamic state. Consider the open fault denoted by an arrow in Figure 2-4. When CP = 1, logic value 1 enters the slave latch at node SD, N4 = 0 and output Q = 0 since transistors MP06 and MN06 are on. When CP switches to low, N5 is driven by Vdd since MP08 is on in the fault-free circuit. Hence N5 and Q hold logic value 1 and 0. In the faulty circuit, SD is floating when CP = 0 but still retains the logic value 1 from the last half cycle (when CP = 1) since SD discharge slowly (assume the open resistance between N5 and F is large enough such that the rate of charging SD is lower than the discharging rate). Thus, Q will remain at 0. Therefore, this fault is not detected. In functional mode of operation, if this flip-flop is not refreshed often enough, it may lose the stored information. This fault turns the scan cell into a dynamic flip-flop. If the clock is toggled often, the faulty scan cell functions properly, even though it is dynamic, since it is refreshed often. However, when clock is shut-off during clock gating, SD is floating. If SD was set to 1 prior to this then the fault will appear when we get out from the clock gating phase. This is a problem if state retention is required. Frequency scaling is another scenario when such faults could manifest themselves due to the current leakage. Such problem is identified in [2.2] and a design of D-latch which can be used to compose flip-flop is proposed. A clocked D-latch shown in Figure 2-5(a) is studied in [2.2]. PFETs P3 and P4 and NFETs N3 and N4 are not detected because of the reason described above. Those faults may be detected by applying tests at very slow speed to let the voltage at node Q1 discharge/charge to the faulty value. However, the time required to reduce the voltage at node Q1 in Figure 2-5(a) depends on the capacitance at this node

and leakage current. In addition, this method increases the testing time which may not be cost-effective. In order to detect such faults, the data and the clock signals are required to be independently controllable. The D-latch shown in Figure 2-5(a) is augmented with an additional controllable input, C, as shown in Figure 2-5(b). During normal operation C is set to 1 and during testing operation C can be changed irrespective of the state of the clock. For example, to detect open fault in P3, the test sequence, T1 (CL = 1, D = 0, C = 1, Q1 = 0), T2 (CL = 0, D = 1, C = 1, Q1 = 0), T3 (CL = 0, D = 1, C = 0, Q1 = 0), T4 (CL = 1, D = 1, C = 0, Q1 = 0), T5 (CL = 0, D = X, C = 0, Q1 = 0) and T6 (CL = 0, D = X, C = 1, Q1 = 0), is applied. However, this design introduces one primary input and four transistors. Hence, it increases the size of the scan cell which is not practical.

Figure 2-4: Open fault turns scan cell into dynamic state

Figure 2-5: D-latch used and proposed in [2.2]

Obviously, stuck-open faults in the serial path are easily detectable, because the output of every gate on the serial path is uniquely set by tests. On the other hand, open faults in the branches in the parallel path are much harder to detect and they represent the main problem. For example, the master latch and latch stage in Figure 2-1 are shown in Figure 2-6. Consider the open faults denoted by arrows in Figure 2-6. They are not detected since one of the transistors in the transmission gate is open will not block the signal propagation from multiplexer to the master latch. To solve this problem, one can change the design shown in Figure 2-7. It is a scan cell implementation where four clocked inverters composed by MP02 and MPX1, MN02 and MNX1, MP06 and MPX2, and MN06 and MNX2 are used instead of the transmission gate between the master latch

and slave latch. By replacing the transmission gates in Figure 2-6 with the clocked inverters as shown in Figure 2-7, those untestable stuck-open faults do not exist. However, this implementation may degrade the scan cell performance. The transmission speeds from multiplexer (DP) to master latch (N1) and master latch (MD) to slave latch (SD) is reduced since two transistors in parallel is replaced by a single transistor between them which increases the resistance.

The problem of undetected opens in parallel branches can also be solved by removing the redundant part of circuit. [2.9] proposed to change the design of a scan cell at transistor level without changing the logic behavior of the circuit. This can be done by identifying the partial redundancies, i.e. those circuit elements that do not cause any change in logic behavior, but cause other behavior changes, e.g., change in timing (signal transition speed). For example, one of the transistors (e.g. MN02) in transmission gate in Figure 2-6 can be removed.

Figure 2-6: Undetected stuck-open faults (SOPs) in Figure 2-1

Figure 2-7: Clocked inverters used

#### 2.4 Summary and remarks

This chapter shows that ATPG patterns only target inputs and outputs of scan cells and do not give high coverages of the defects internal to the scan cells. Those faults not detected may lead to functional failures or pose reliability issues. It had been shown that IDDQ tests were effective to detect a large portion of scan cell internal faults. Especially for large resistance bridging faults, the faults may not be detected by logic testing because the two bridged nodes may take the fault-free logical values. However, as feature size of VLSI decreases (45nm is coming up), the faulty quiescent current is too small compared to the total chip nominal current. Determining the current limit to differentiate faulty and fault-free circuit is crucial and difficult since it is a dynamic value depending on bridge resistance, power supply voltages and transistor threshold voltages, etc. Thus, the IDDQ only detectable faults will become an important contributor to test escapes.

In addition to the fault coverage, testing cost in terms of test pattern size is another major concern to detect scan cell internal faults. Some methods such as checking sequence based tests reviewed in this chapter are not practical due to the large size of tests and difficulty to generate the tests.

Changing the scan flip-flop design or layout may be an alternative method to improve the scan cell testability. However, the considerable overhead area added and cell performance degradations introduced by the new designs are critical issues need to be carefully considered.

# CHAPTER III ON DETECTABILITY OF SCAN CELL INTERNAL FAULTS USING STUCK-AT AND STUCK-ON FAULT MODELS

Stuck-at fault model has been extensively used in the industry to mimic defects at lines and nodes in circuits. Defects in transistors are usually modeled by stuck-on fault model. In this chapter, we present the first step in developing an alternative test methodology for scan cell internal faults by using stuck-at and stuck-on fault models. A new flush test is proposed to improve the stuck-at and stuck-on fault coverage. Other conventional methods, IDDQ testing and low power supply testing, are also investigated to cover the identified coverage gaps. Experimental results on a standard scan cell used in a 90 nanometer industrial design are included.

#### 3.1 Introduction

As shown in Chapter I, there are a large number of faults residing in scan cells. Thus, it is important to determine the coverage of faults internal to scan cells and if necessary investigate cost effective methods to augment tests generated by standard automatic test pattern generation (ATPG) procedures to improve coverage of scan cell internal faults.

In this chapter we report the results of a case study on an industrial design. We report fault coverage using standard test patterns and flush tests. The study exposes test coverage holes that need to be addressed. We also propose a new flush test called half-speed flush test that closes some of the coverage holes. In order to achieve the defect coverage or lowest Defects Per Million tested devices (DPMs), the defect behaviors need to be described as accurately as possible. Such defect behaviors are described by many fault models. In this chapter, we focus on detection of stuck-at faults (SAFs) and stuck-on faults (SONs) internal to scan cells.

It has been noted that many faults internal to latches and flip-flops may not be detected [3.3-3.11] by standard scan based tests. In Chapter II, we reviewed a checking

sequences based test method and showed that it is not practical due to the large size of tests generated and difficulty to generate the tests.

Noting that some of the transistor stuck-on faults cannot be detected by voltage based tests, a testable design of latches was proposed by Aissi and Olaniyan [3.11]. Use of this design increases the area of scan cells and requires two additional primary inputs to control internal nodes of scan.

The goal of our work is to investigate the use of standard scan cells and existing methods of generation and application of scan based tests to detect scan cell internal faults. In this chapter we present results of the first step in this direction. The main contributions of the work presented are:

- (1) Defining the notion of half-speed flush test and demonstrating that half-speed flush tests increase coverage of internal faults in scan cells.

- (2) Demonstrating that existing test generation and test application methods together with the half-speed flush test cover cell internal faults to similar degree as the checking sequence based tests.

- (3) Showing that IDDQ testing of 90nm and beyond designs may not be feasible for a significant portion of the faults leaves coverage holes which, in addition to the issue of quality of shipped products, could result in a serious reliability risk.

We quantify the above using a 90nm commercial product described in Table 1-1 which consists of approximately 4.3 million cells and 54 million transistors.

The remainder of the chapter is organized as follows. In Section 3.2 we briefly discuss related earlier works on the detection of scan cell internal SAFs and SONs [3.5-3.10]. The stuck-at and stuck-on fault models and some test methods for such faults are also reviewed. In sections 3.3 and 3.4 we discuss the half-speed flush test we defined and the probabilistically detected faults. In Section 3.5, we present the HSPICE simulation

results on scan cell internal faults and discuss the conclusions from the simulation results. Finally, Section 3.6 concludes this chapter.

# 3.2 Preliminaries

In this section we briefly review the stuck-at and stuck-on fault models. The conventional test methods targeting these faults are also presented. In addition, we will discuss some related earlier works on the detection of faults in scan cells applying these fault models.

#### 3.2.1 Stuck-at and stuck-on fault models

Fault models are abstraction of defect behaviors and test patterns are generated by targeting certain fault models which describe the defects as accurate as possible. The investigations in this chapter focus on scan cell internal faults using stuck-at and stuck-on fault models.

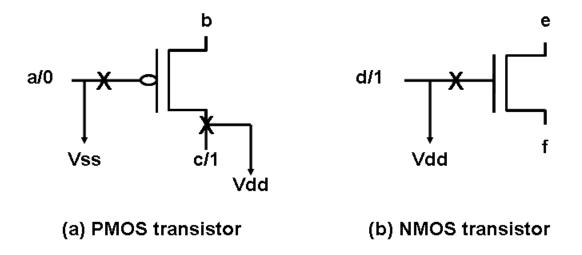

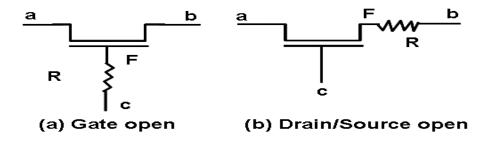

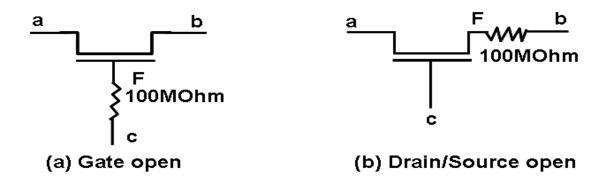

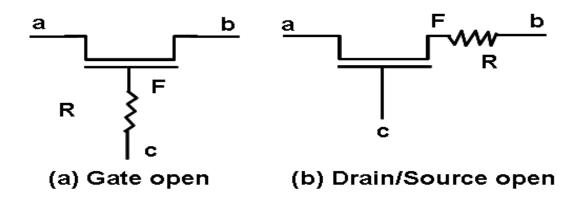

**Stuck-at fault model** is the most widely used fault model in which represents a single line being permanently stuck at a logic value (1 or 0) which is caused by unwanted shorts between the line and power supply (Vdd) or ground (Vss). Figure 3-1(a) shows that the gate (node a) of a PMOS stuck-at 0 and the source (node c) stuck-at 1 faults. This fault model is independent of the technology, as the concept of a wire being stuck at a logic value can be applied to any structural model. It was also been found that the tests based on this model detect many unmolded defects.

In addition, the stuck-at fault model can be used to model other types of defects. For example, NMOS transistor **stuck-on fault** where the faulty transistor is permanently turned on can be modeled by the gate of the NMOS transistor stuck-at 1 shown in Figure 3-1(b). Note that when counting nodes for considering scan cell internal faults, stuck-at fault model may not consider fan-out branches. For example, although node N4 has two branches in Figure 2-1, only two stuck-at faults (N4 stuck-at 1 and N4 stuck-at 0) are

considered. N4 stuck-at-0 makes transistors MP08 stuck-on and MN08 stuck-off. This is different from the gates of MP08 and MN08 stuck-at-0 independently. The stuck-on fault can be caused by intra-gate shorts (the shorts between the drain and the source of the faulty transistor) and gate to power supply shorts.

The stuck-at fault model has been extensively used in industry for decades. For the detection of single stuck-at fault, we must activate the fault by setting the logic value opposite to the faulty value at the faulty site. For example, to activate the fault a/0 in Figure 3-1(a) the node a is set to 1 which involves the line justification. The line-justification problem deals with finding an assignment of primary input values that results in a desire value setting on a specified line in a circuit. The controllability is used to measure the difficulty of setting a line to a value. In order for the detection of a fault, fault propagation is required where primary inputs are set to appropriate values such that the fault is able to propagate to at least one of the primary outputs (i.e., one or more primary outputs present the faulty value due to the fault). The ability of fault propagation is measured by the observability which indicates the relative difficulty of propagating an error from a line to a primary output.

The detection of defects applying stuck-on fault model is similar to the detection of stuck-at fault. Instead of activating the fault by setting fault-free value at the faulty site, the gate of the faulty transistor is set to 0 for NMOS and 1 for PMOS which attempts to turn off the faulty transistors.

#### 3.2.2 Previous related work

A checking sequence based tests [3.6-3.9], discussed in Chapter II, have the advantage of independent of scan cell implementation. A sequential ATPG is required

even for full-scan circuits. The complexity of the sequential test generation process restricts its use to small circuits.

Applying checking sequences based tests to muxed-input scan cell shown in Figure 3-2, the following fault coverage was obtained in [3.8]: 31 out of a total of 32 (96.9%) SAFs and 18 out of a total of 26 (69.2%) stuck-on faults (SONs) are detected without using IDDQ. With IDDQ testing, one more SAF and 5 additional SONs are detected, thus making SAF coverage 100% and SON coverage 88.5%.

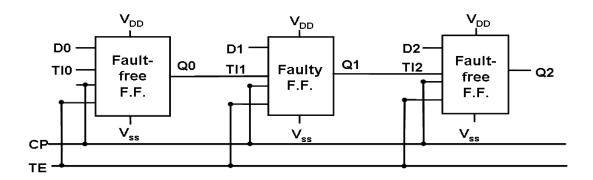

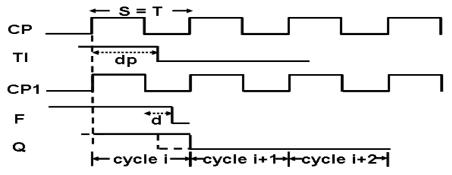

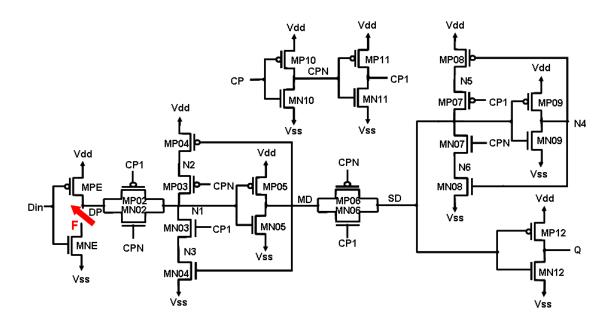

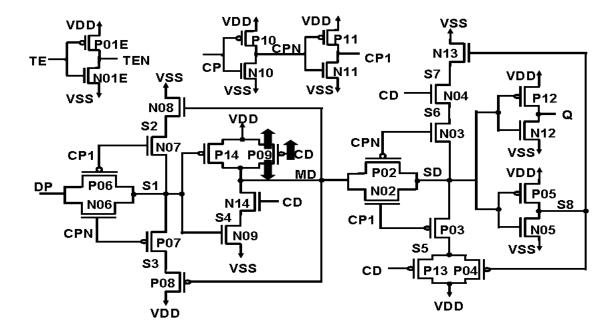

# 3.3 Half-speed flush test

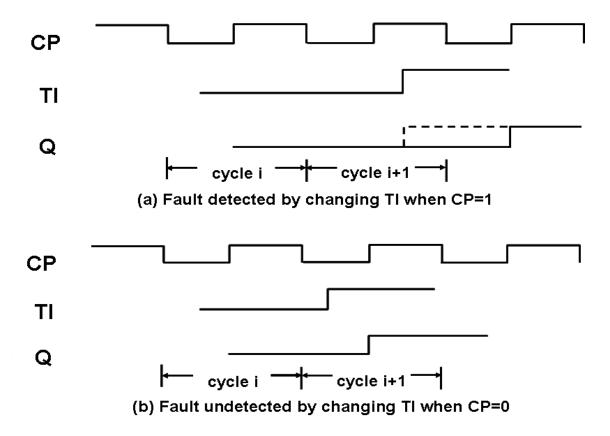

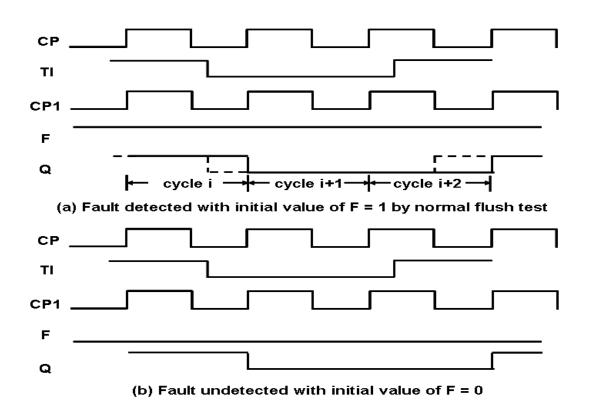

Scan input TI (cf. Figure 3-3) of a single flip-flop in a scan chain gets its value from the output of the previous flip-flop which changes value at shift clock rising edge. There is a path delay between the two stages. Thus TI can change value either within the half cycle where CP = 1 if the path delay is less than half shift clock period or the half cycle where CP = 0 when the path delay is greater than half of the shift clock period. In the fault-free circuit a new value can propagate to the output of a flip-flop only when it arrives within CP = 0. However, we found that detection of some cell internal faults require that scan input TI change when CP = 1. To detect such faults we define a new type of test called *half-speed flush test*. For example, Figure 3-3 shows line CP1 stuck-at-0 (highlighted by arrows on the fan-out branches of CP1). This fault makes transistors MP02 and MP07 to be always on and transistors MN03 and MN06 to be always off. We refer to Figure 3-3 and Figure 3-4 in the following discussion of this fault.

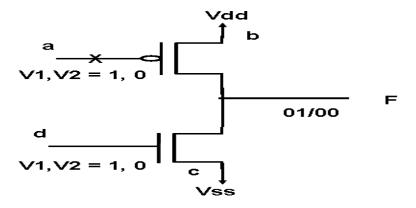

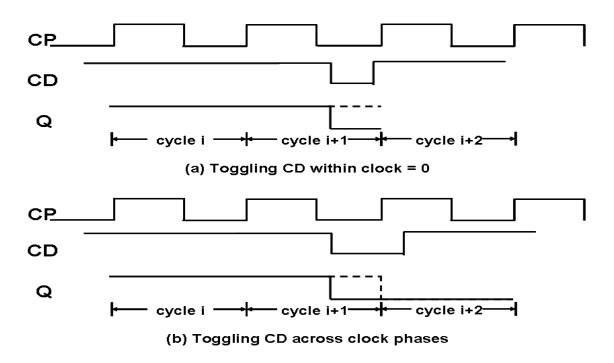

To detect CP1 stuck-at-0 fault, we can first set Q to 0 in clock cycle i by setting TI to 0 when CP = 0. After that we set TI to 1 in clock cycle i+1 when CP = 1. In the fault-free circuit, this change of TI in shift clock cycle i+1 will not propagate to Q, since MP02 and MN02 are turned off when CP = 1. However, in the faulty circuit, this change in TI, during clock cycle i+1, will propagate to Q in clock cycle i+1, since MP02 is on due to the fault and MP06 is on since CP = 1. This is shown in Figure 3-4(a), where solid

lines are signals from fault-free circuit and dashed lines show faulty waveforms. By a similar argument, as shown in Figure 3-4(b), we note that if instead of changing TI when CP = 1 in clock cycle i+1 we change TI when CP = 0, then the fault will not be detected.

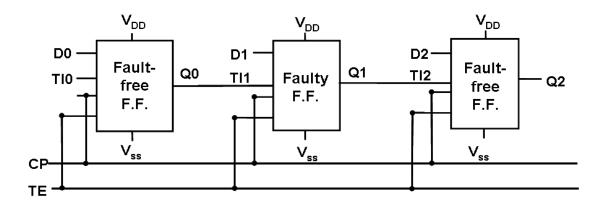

Detection of faults by changing TI when CP = 1 poses a problem. During test application we will not be able to change TI directly, but indirectly through the output of the previous flip-flop in the scan chain. We next discuss a method to accomplish this.

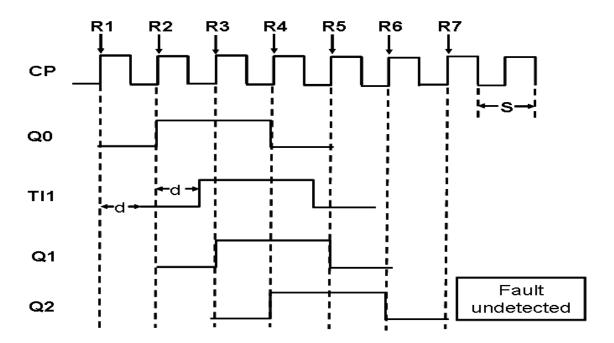

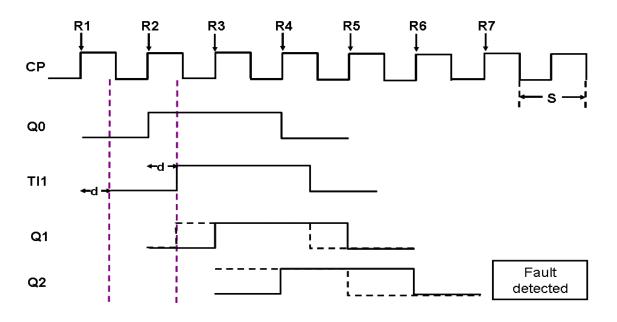

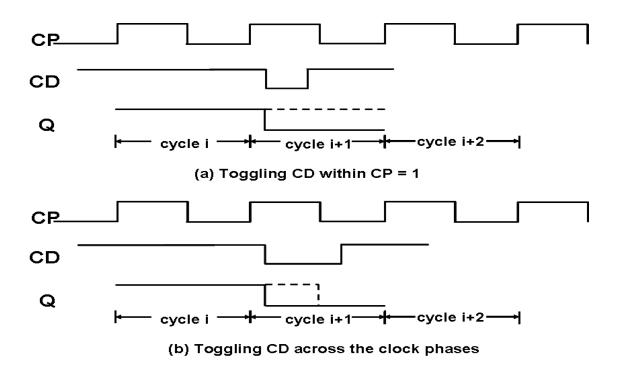

In Figure 3-5 three MD flip-flops are cascaded to form a segment of a scan chain. Assume the fault discussed above occurs in the second scan flip-flop of Figure 3-5. TI1 gets its value from the previous scan flip-flop output (Q0) in the scan chain. There is a path delay between Q0 and TI1. Assume that the shift mode of the scan chain has been closed during timing closure for f mega hertz (i.e. the maximum delay between Q0 and TI1 is T = 1/f). Then the propagation delay (d) from Q0 to TI1 lies between 0 and T. Let us assume that the shift clock period is S. Q0 = 00110 (a segment of flush test), is produced at the shift clock rising edge. Therefore, TI1 changes within CP = 1 if d is smaller than S/2. As discussed previously, if the path delay results in TI1 transition within CP = 1, then this fault can be detected by the flush test. Whereas the fault cannot be detected if d is greater than S/2, causing TI1 to change within CP = 0. Figure 3-6 shows the waveforms when the shift cycle time S = T. The path delay between Q0 and TI1 is greater than S/2 causing TI1 to transition within CP = 0. By observing outputs of scan flip-flops Q1 and Q2, as discussed above, the fault is not detected. But, we can expand the clock until TI1 transitions within the half cycle with CP = 1. This can be accomplished by slowing down the scan shift speed during the application of the flush test 00110011.... Figure 3-7 shows that the fault is detected by applying the flush test with scan shift cycle period S = 2T. The dashed lines show faulty waveforms and the solid lines are fault-free waveforms. Starting from rising edge R3, faulty value (00110/11100) of Q2 is generated. This flush test with shift clock period S no less than

2T detects the fault with path delay both greater and smaller than T/2. S = 2T is preferred in order to maximize the flush test shifting speed.

This motivated our definition of half-speed flush test. Assume that we have timing closure of scan chain at frequency f, then the shift speed for half-speed flush test will be at frequency f/2 or less. For example, if timing is closed at 10 mega Hertz (200 MHz) half-speed flush test runs at 5 mega Hertz (100 MHz) or less. Note that we only slow down the flush test 00110011....

In [3.8], the authors discussed slow speed application of the checking sequences. The motivation for that was to detect additional stuck-open faults (SOPs). In [3.8], the above mechanism of detecting such scan cell internal faults using flush tests was not considered. Furthermore, the frequency for the test we are proposing is related to the timing closure frequency of the scan chains of the design.

# 3.4 Probabilistically detected faults

Probabilistically detected faults are faults that are not proved to be detected but have a high probability of detection. Consider node N19 stuck-at-1 highlighted by an arrow in Error! Reference source not found. Error! Reference source not found.. The detection condition for this fault is D = 0, TE = 1, TI = 1, Q = 1. Since TE = 1, it cannot be detected by a scan cell boundary SAF test. Assume that initially the scan chain has random bits and the length of the scan chain is L. Consider the case when the flush test 00110011... is applied to the scan chain. Data input D, which is driven by the combinational logic, can be either 0 or 1. If we assume that D = 0 or D = 1 with equal probability, then the probability that N19 stuck-at-1 is not detected by the flush test is  $(4/5)^L$ . When the flush test of all ones is applied, the probability that the fault is not detected, under the same assumptions on D, is  $(1/2)^L$ . In typical industrial designs L can be about 1000. Thus the fault can be assumed to have been detected by the flush test. In this work we say that the fault is assumed probabilistically detected. We perform such

probability analyses to identify faults which can be classified as probabilistically detected.

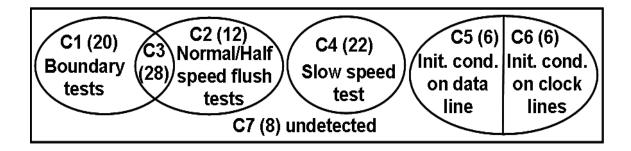

# 3.5 Experimental Results

In our HSPICE based simulation, we used the segment of a scan chain shown in Figure 3-5. A target fault is injected into the second scan cell by modifying its circuit description. To simulate SAFs, we connect the faulty node to Vdd (stuck-at-1) or to Vss (stuck-at-0). A SON is modeled by connecting the gate of a faulty NMOS transistor to Vdd and the gate of a faulty PMOS transistor to Vss. There are a total of 44 SAFs and 34 SONs. Table 3-1 summarizes the simulation results. The number of faults detected by normal speed flush test, with the corresponding percentage is shown in column 2. The additional number of faults detected by half-speed flush test is shown in column 3. It is important to note that even though we do not explicitly show this in Table 3-1 all faults detected by the flush test 00110011... applied at normal shift frequency are also detected by the half-speed flush test. Thus one only needs to apply the flush test at half-speed to detect all the faults reported detected by the flush test. Column 4 shows the number of faults not detected by flush test and detected by scan cell boundary SAF tests. Fifth column shows the number of probabilistically detected faults. The last column gives the total number of undetected and IDDQ only detectable faults. The second row is the results for SAFs. Results for SONs are presented in the row 3, respectively. Next we discuss each of these rows in details.

From Table 3-1 we observe that 34 (77.3%) out of 44 SAFs are detected by flush test, and another 1 (2.3%) fault is detected only by the half-speed flush test. Third column shows that boundary SAF tests detect 5 (11.3%) additional SAFs that are not detected by the two flush tests. Four faults (9.1%), N19 stuck-at-1, N20 stuck-at-1, TE stuck-at-1 and TE stuck-at-0, are probabilistically detected. We compare this result with D flip-flop results from [3.8]. Out of a total of 24 SAFs one fault was not detected by the checking

experiments and required IDDQ testing. In our case, all SAFs are detected without IDDQ, assuming that the probabilistically detected faults are indeed detected. Given the uncertainty of using IDDQ for future technologies, removal of this dependency on IDDQ tests is a significant step forward. Half-speed flush test also increases SAF coverage by 2.3% for a cell and by 1.03% for the full-chip using the data for the industrial design in Table 1-1. Given that today's designs attempt to achieve over 99% coverage this increase is quite significant.

From Table 3-1 we note that the flush test detects 11 (32.4%) and another 3 (8.8%) SONs are covered by half-speed flush test. Scan cell boundary SAF tests detect 1 (2.9%) additional fault. The faults MN01B, MP01A and MN01E stuck-on faults are probabilistically detected. The remaining 16 (47.1%) SONs are not detected by Boolean tests. However, 12 (35.3%) of these faults can be detected by IDDQ testing if such measurements are feasible. Comparing with the results from [3.8], 4 out of a total 20 SONs in the D flip-flop considered in [3.8] were not detected by the checking experiment based tests. If we restrict ourselves to the two latches of the MD flip-flop used in our design, we get the same coverage as [3.8] but without using the long checking sequences. Once again note the importance of the half-speed flush test. It added about 8.8% SON coverage per cell.

#### 3.5.1 Coverage gaps identified

The last column of Table 3-1 shows that fault coverage gaps still exist. Many of them are IDDQ detectable only. By simulating a scan cell using HSPICE we determined that for all the IDDQ only detectable faults, the IDDQ through the transistor affected by a fault is within  $1\mu A$  when the fault is not present and the IDDQ is in the range of  $47.71\mu A$  to  $365\mu A$  in the presence of the fault. For the 90nm product under study the faulty IDDQ is less than 0.04% of the nominal total chip IDDQ. Hence, we believe that full chip IDDQ based measurements will not detect such defects.

We note that many of the defects that require IDDQ testing will be activated during the functional mode of operation. Consider the example in Figure 3-8 where MN01C SON is highlighted by a dashed circle. For MN01C SON the test condition is D = 0, TE = 0, TI = 1, Q = 0. A Vdd to Vss path is formed in the multiplexer. IDDQ for fault-free circuit remains as low as  $1\mu$ A, whereas it is  $47.8\mu$ A for this faulty circuit. Note that this condition will be satisfied during the functional mode of operation. Whenever this condition is satisfied MP01A and MP01B sink about 47 times more current. This current surge is a major reliability issue for these transistors.

Using the data in Table 1-1, we estimate that the percentage of IDDQ only detectable SONs is approximately 35.3% of the transistors in the logic. This poses a potential reliability risk if not addressed.

An alternative to detecting such defects could be low voltage testing. For the fault in Figure 3-8, we performed a simulation and the results are given in Table 3-2. In order to detect the fault, the supply voltage was progressively lowered. Note that only when the supply voltage was reduced by more than 50% the output showed a faulty value. However, lowering voltage by more than 50%, we believe, is not feasible and therefore low voltage testing cannot be used. An alternative test for such defects is thus required.

We performed probabilistic analysis using simple assumptions and found that 9.1% and 8.8% of SAF and SON of the cell faults are probabilistically detected shown in column 5 in Table 3-1. Translated using the data from Table 1-1, this implies full-chip coverage of 4.08% SAFs and 3.83% of SONs. Considering desired SAF target coverage in the high nineties this is very large. It is therefore important to determine what percentage of the probabilistically detected faults is actually detected. Additional tests may be required to cover any coverage gaps found.

# 3.6 Conclusions

The detection of scan flip-flop internal faults is important as it may result in functional failure. Nearly 50% of the SAFs reside in the scan chains and are currently not directly targeted for test generation. The earlier proposed method of using checking experiment [3.8] to detect these faults is not practical because of its large size and the difficulty of deriving the tests. An analysis of SAFs and SONs in a MD flip-flop using flush tests and boundary stuck-at tests was presented in this chapter. We proposed a new flush test called half-speed flush test and showed that it improves fault coverage by a couple of percentage. We also identified that a large proportion of faults are probabilistically detected. It is important to verify with product data if these faults are actually detected by the ATPG and flush tests. We showed that there is also a large class of IDDQ only detectable faults that poses a serious reliability risk. Given these gaps, we believe, alternative tests to detect these faults are required.

Table 3-1: HSPICE simulation summary

|     | Normal     | Half-speed | Boundary  | Probabilistically | IDDQ        |

|-----|------------|------------|-----------|-------------------|-------------|

|     | Flush Test | Flush Test | SAF Tests | Detected          | /Undetected |

| SAF | 34         | 1          | 5         | 4                 | 0           |

|     | 77.3%      | 2.3%       | 11.3%     | 9.1%              | 0%          |

| SON | 11         | 3          | 1         | 3                 | 16          |

|     | 32.4%      | 8.8%       | 2.9%      | 8.8%              | 47.1%       |

Table 3-2: Low Vdd testing of MN01C SON fault at 25°C with test: D = 0, TE = 0, TI = 1, Q = 0

| Vdd | 1V | 0.8V | 0.7V | 0.42V |

|-----|----|------|------|-------|

| Q   | 0  | 0    | 0    | 0.42  |

Figure 3-1: Stuck-at fault model

Figure 3-2: Scan cell used in [3.8]

Figure 3-3: Fault CP1 stuck-at-0

Figure 3-4: Detection of the fault CP1 stuck-at-0

Figure 3-5: Logic diagram of a scan chain with length 3